# What is a Printed Circuit Board Pad?

What is a printed circuit board pad, it may sound like a dumb question but do you stop to think what it really does and how its size is defined and why?

A printed circuit board pad provides an electrical connection point and a surface which can be used to mechanically bond component terminations and is the interface to the laminate surface. Here we illustrate the types of pads used in the design world and some of the special requirements for manufacture.

#### **Conventional Single Sided Pads**

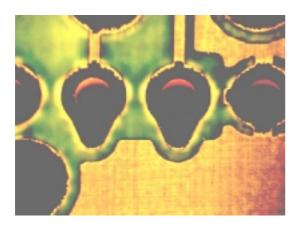

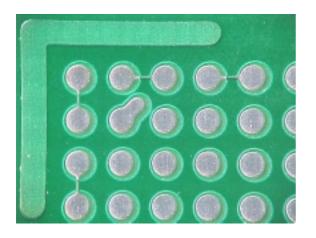

The pads are normally always round but in the past they have also been produced as oblongs or squares. Some companies produce pads as a pear shape and the conventional through hole leads are clinched along what is the narrow end of the pear shaped pad. This sometimes indicates the direction of clinch, and used as a visual reference for the correct clinch. It normally occurs on single sided boards and does increase the surface area of the pad and its adhesion to the board.

Pear shaped pad on a single sided board

The size of the pad comes from the hole size as it is the only mechanical bond available and of course the electrical interconnection. As a guide the hole size is determined by the component lead diameter. Leads are either round, square or oblong and it is the largest dimension that needs to be considered. The lead diameter, the dimension across the corners on square or oblong leads, would be the basis for any calculation. Typically the holes will be 0.040 0.045"

Another key issue is the required hole tolerance to allow automatic assembly of the through hole leads. If automatic assembly is to be used this is normally defined by the equipment supplier. As an example the lead dimension plus 0.010" would be the minimum dimension. In the case of single sided non plated through hole boards this dimension is important. As the hole to lead ratio goes up the solder joint strength is reduced. This has far more impact than the pad size.

The solder mask aperture would be 0.004-6" larger than the pad size when using photo imagible solder masks which is now standard in the industry. There are of course exceptions to this but they are limited. If screen printable solder masks are used it is good practice to double the aperture clearance.

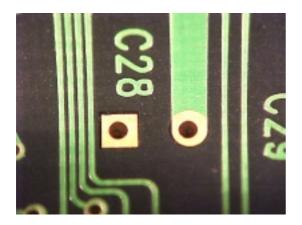

Solder joint failure due to incorrect hole to lead ratio

## Plated Through Hole Pads

Basically the dimensions for the plated through hole are the same as for single sided boards. As the though holes are plated after drilling then a calculation should be made based on the amount of copper to be deposited in the through hole, typically a minimum of 25um. The minimum finished hole size for automatic assembly would again be the pin size plus 0.010". The pad should be defined based on the soldering process to be used. As a basic guide the pad size may be approximately 0.065", however this has less impact on the strength of the solder joint as all the strength lies in the barrel of the hole.

With the use of lead-free alloys where lead may be a contaminate modifications to the size of pad and the resist aperture have provided a solution to fillet lifting. The problem of fillet lift relates in the uneven solidification of the solder in a plated through hole board and the surface of the pads.

It has been recommended by some Japanese companies to place the resist over the pad on the board surface. This reduces the amount the solder fillet wets out from the barrel of the hole. This can be applied to both sides of the board, However, the problem of fillet lifting during wave soldering is generally seen only on the topside of the board unless through hole or intrusive reflow are being used during assembly. In the case of through hole reflow it can happen on both sides. The authors trials have not found this design change to work, you still see fillet lifting.

One final point is the orientation of components in a board. If the parts must be orientated in a specific way for electrical reasons the positive or pin one is represented by a different shape of pad. If the pads are normally round the orientation mark can be a square pad.

#### Pad shape being used to show the orientation of component

Although not standard practice a nice fix to a problem board which always features shorts in the centre of the board is changing the resist on the pad. In the example below the last two trailing pads on a large socket have had the pads resist coated a second time. This reduces the possibility of solder shorts forming. There are some problems that can be more easily solved with design than process. The bottom line is what is the cost of eliminating process defects where you have a large number of board to process and you also have a PCB manufacturing facility on site!!!!

#### Via Hole Pads

A via hole is a connection through the board or only partly through the board. They are used to make interconnections but not required to have leads soldered in the holes. The via hole size normally ranges between 0.006" - 0.010" in a pad 0.014". Via holes can have the same solder mask apertures as plated through hole which is 0.004-6" larger than the pad.

Via holes can also be capped with solder resist or plugged with other materials prior to covering the board with resist. A key feature of any plated through connection is good quality through hole plating of the required plating thickness. If there is any outgassing in the hole during soldering it will cause the resist to lift or pop. If the via is filled with solder it can also cause solder balls on the via holes.

A further alternative is to take the resist image over the via hole, although not capping or covering the hole it seals the edge of the pad. This prevents shorts forming between the via and other locations particularly under BGA and CSP parts. It is good practice to do the same on the base of the board. If the vias are to be used for test access, on the bottom side do not leave all holes open as their tight proximity can lead to micro shorts forming; coating alternative locations is good practice.

Via in pad is becoming more common practice in design today. In this case the via is produced by laser and is barely visible on the surface of the pad. Larger via in pad designs can be a problem with solder paste printing and reflow. Using pulse plating can fill the via holes eliminating this issue.

#### **Test Pads**

A test pad will normally be a round or square pad which can be placed as part of a track. The size of the test pad is defined by the accuracy of the test fixture and pin type used. The test pin type may also define the resist aperture size as crown pins can hang over the edge of the pad and contact the resist rather than the pad leading to intermittent connections. This can occur when the solder resist is thicker in selected areas of the board. This can also lead to wave solder skips which often occurs on test pads leaving them with a surface which may not offer the same contact resistance during test. A typical pad size for test access may be 0.012-0.018"", it is common today to see surface pads used as test points during printed circuit board fabrication with their characteristic contact marks.

#### Wave Solder Surface Mount Pads

Surface mount wave solder pads are normally square or oblong and are defined with the component in mind and the separation distance of the pads. The pad distance is selected due to the relative position of the component terminations and the need for adhesive to hold them in place.

The position and the length of the pad will depend on the height of the component; this is due to the displacement of the solder by the body of the component which is not wettable with the solder. Changing the standoff height of the component by a few thousands of an inch can increase the incidence of solder skips which are unwetted pads. This is often seen on one design where different vendor parts are used in production.

Solder skips during wave soldering can also occur due to gassing on the base of the board when the wave contacts the board or due to variations in the wave height between boards being processed. The incidence of skips is exaggerated by the size of the pads, the smaller the pads for chips or SOT23 devices increases the possibility of unsoldered pads. The key feature for these devices is to lengthen the pads, not increase the width of the pads. The increased length helps the pads protrude from the component body reducing the possibility of solder displacement.

In the case of SOIC, TSOP and QFP solder shorts becomes the issue this is normally associated with pads that are too wide. As an example the SOIC termination has a nominal width of 0.018" and the pad width of 0.024-0.028" which will lead to shorts; dropping the pad width to 0.020-0.022" will improve the yield. Just try measuring some of your own boards in production. Measure the pad sizes on boards where you get shorts and those that you do not!

## **Reflow Pads**

Reflow pads are generally smaller than wave solder pads and the key feature is the size and distance of pad separation. During reflow the solder must not cause significant movement of the part due to the wetting forces on the terminations. The wettable terminations on the component should have a neutral position on the pad surface. If during wetting they pull in any direction it increases the possibility of component twist or lift.

The pads for each device should have equal dimensions to eliminate a difference in forces on the terminations during soldering. If the pads vary in surface area they can again promote component movement due to unequal wetting forces. As the size of the pads becomes less than the surface area of the chip termination like 0201 chip parts, the problems of movement are exaggerated. Different volumes of paste on the pads can also affect the time of reflow on each termination.

# **Ball Grid Array Pads**

BGA pads are round with tracks leading off for further connection to vias or other surface contacts. The pads often take their size from the pad size on the actual device and this is a good starting point. Normally with BGA pads of 0.020 - 0.025" the track size would be either 0.006-8". With blind, buried, capped vias it is also possible to have the connection below the pad surface.

The resist is left relieved from the pad not over the pad. As a guide the resist gap will be 0.002-3" to allow for the tolerances of printed board manufacture. There are design rules still circulating in the industry which show resist defined pads but this is considered poor practice.

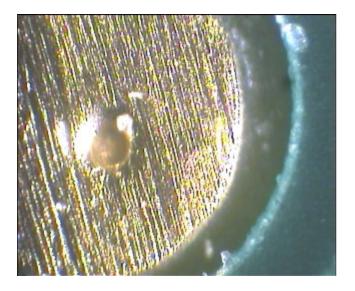

# Via in pad being used as a direct interconnection to the inner layer

BGA pads may also incorporate wetting indicators to allow solder wetting to be easily assessed by X-ray inspection. These pad changes may be incorporated on to selected pads on the four corners of the array and on the centre of the package. The reason for different areas is to show complete reflow in both the outer and inner areas. Normally the centre pads of the BGA are the last to reflow during soldering.

BGA pad with a wetting indicator, a little larger than necessary but it does show the wetting under xray inspection

## Chip Scale Package Pads

CSP pads are normally round between 0.010-0.012" with standard separation gap for solder resist windows of 0.004-6" larger that the pad size. With many CSPs being used on thin substrates there are concerns over the strength of the overall joint. Making the pads larger or putting resist over larger pads all increase the adhesion to the laminate.

The use of blind or capped vias under the pad also act as an anchor for the pad, increasing the adhesion dramatically. Capped vias are better than open on the mounting pads as these reduce or eliminate voids in the already small joints.

For further information on design for manufacture visit our web site www.bobwillis.co.uk which provides information on our interactive CD-ROM "Printed Board Design for Manufacture and Defect Guide" and videos on printed board design. Bob Willis is a process engineer providing engineering support in conventional and surface mount assembly processes. He runs production lines for suppliers at exhibitions and also provides seminar and workshops world wide. Bob has one of the largest collection of training videos, interactive CD-ROMs and training material in the industry. Bob will be presenting four Master Classes at APEX in California, he will also be presenting classes at SMT Nuremberg in Germany for those engineers visiting the show. For further information on how Bob may be able to support your staff contact him via his web site www.bobwillis.co.uk

Don't forget to pass this paper on to a friend!