# Interfacing the H8/3644 to a Serial $E^2$ PROM

How to use the SCI Interface to emulate an SPI interface

## HITACHI

Revision 1.1 8/4/98 Hitachi Semiconductor (America) Inc. Leonard Haile

## Notice

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## Contents

## Summary 1

| Section 1 Introduction                        |

|-----------------------------------------------|

| 1.1 Serial E <sup>2</sup> PROM Overview       |

| 1.2 SPI Overview                              |

| Section 2 SPI Details                         |

| 2.1 SPI Pin Descriptions                      |

| 2.2 SPI Transfer Formats                      |

| Section 3 SPI E <sup>2</sup> PROM Details     |

| 3.1 The Commands                              |

| 3.2 The 25xx040 E <sup>2</sup> PROM           |

| 3.3 Protocol                                  |

| 3.3.1 Read Command Bus Timing                 |

| 3.3.2 Write Command Bus Timing                |

| 3.3.3 Write Command Polling                   |

| Section 4 SCI1 Operation                      |

| 4.1 Hardware Registers                        |

| 4.2 Data Transfer Operations                  |

| Section 5 Test Hardware                       |

| Section 6 Software Details                    |

| 6.1 Bit Reverse Function                      |

| 6.1.1 Example Declaration12                   |

| 6.1.2 Design Tradeoffs                        |

| 6.2 E <sup>2</sup> PROM Interface C Functions |

| Appendix A Code16                             |

| Appendix B Header Files                       |

## Summary

This application note provides assistance and source code to ease the design process of interfacing a Hitachi H8/3644 microcontroller with a Serial Peripheral Interface (SPITM) compatible serial E<sup>2</sup>PROM. The Serial communication interface 1 (SCI1) hardware on the H8/3644 provides a simple three-wire connection to an SPI serial E<sup>2</sup>PROM. No external "glue" hardware logic is required, but there are two design issues that the system designer must address.

- SCI1 latches receive data at the rising edge of the serial clock. SCI1 outputs transmit data from one falling edge of the serial clock until the next rising edge. To meet these timing requirements, a designer must specify a SPI serial E<sup>2</sup>PROM that uses the clock polarity/clock phase settings for Mode 1,1.

- 2. SCI1 transmits and receives data starting from the least significant bit. SPI serial E<sup>2</sup>PROMs transmit and receive data starting from the most significant bit. For proper operation the H8/3644 application firmware must provide a function to reverse the data bits.

This application note addresses these two issues. First, background information on the SPI interface is provided to clarify the hardware specifications and make choosing an SPI serial E<sup>2</sup>PROM straightforward. Secondly, an example hardware design with software is provided to reduce the system designer's learning curve.

SPITM is a trademark of Motorola Corporation.

1

## Section 1 Introduction

#### **1.1** Serial E<sup>2</sup>PROM Overview

Many microcontroller applications today need a small amount of non-volatile memory to store some data when the power is off. Serial  $E^2$ PROMs are a popular choice for this non-volatile storage because they have the following characteristics:

- low cost

- small size

- low I/O pin count

- High write/erase endurance

- byte level addressing

- low power consumption

Serial E<sup>2</sup>PROM devices are available in a variety of densities, operating voltages, and packaging options. E<sup>2</sup>PROM vendors offer a full line of serial E<sup>2</sup>PROMs covering several industry standard serial communication protocols. When you look through the data sheets, the various serial E<sup>2</sup>PROMs are listed as two-wire, three-wire, and SPI interface devices. A 2-wire interface product conforms to the I<sup>2</sup>CTM bus hardware specification. A 3-wire product conforms to the MICROWIRETM specification. An SPI interface product conforms to one the several modes possible under the SPI hardware specification.

I<sup>2</sup>CTM is a trademark of Phillips Corporation

MICROWIRETM is a trademark of National Semiconductor Corporation

#### 1.2 SPI Overview

SPI is a general purpose synchronous serial interface. During an SPI transfer, transmit and receive data is simultaneously shifted out serially and shifted in serially. A serial clock line synchronizes shifting and sampling of the information on two serial data lines. Motorola created the SPI port in the mid 1980's to use in their microcontroller product families. The SPI is mainly used to allow a microcontrollers to communicate with peripheral devices such as E<sup>2</sup>PROMs, A/D converters, and displays.

The SPI port is similar to the MICROWIRE interface created by National Semiconductor for their microcontrollers. Both interfaces use similar command protocols, however, SPI devices clock data in and out differently from the MICROWIRE devices. MICROWIRE devices clock data out and in on the same clock edge. SPI bus devices clock data in and out on opposite edges of the clock.

## Section 2 SPI Details

#### 2.1 SPI Pin Descriptions

The SPI interface between a microcontroller and serial E<sup>2</sup>PROM has three lines that control data transfer and one general purpose I/O pin to control the E<sup>2</sup>PROM's chip select. The names used for the SPI hardware lines can vary from one manufacturer's data sheet t to the next. Motorola calls their data out line MOSI (Master Out Slave In) and calls their data in line MISO (Master In Slave Out). Most of the data sheets from other manufacturers call these lines SO and SI. Table 2.1 is a summary of the SPI pin names from several manufacturers.

| Manufacturer      | Clock            | Data In | Data Out        |  |

|-------------------|------------------|---------|-----------------|--|

| Motorola          | SCK              | MOSI    | MISO            |  |

| Hitachi (H8/3644) | SCK <sub>1</sub> | SI      | SO <sub>1</sub> |  |

| Microchip         | SCK              | SI      | SO              |  |

| Xicor             | SCK              | SI      | SO              |  |

| SGS-Thomson       | С                | D       | Q               |  |

#### Table 2.1 SPI Pin Names

Serial E2PROMs that have data lines labeled DI and D0 are MICROWIRE parts and are not compatible with the synchronous serial port on the H8/3644.

#### 2.2 SPI Transfer Formats

For general purpose SPI microcontroller hardware, software can select one of four combinations of serial clock phase and polarity using two bits in a SPI control register. The clock polarity (CPOL) control bit selects an active high or active low clock. The clock phase (CPHA) control bit selects when the data in line is sampled and when the data out line is updated. The clock phase and the clock polarity must be the same for both the microcontroller and the specified SPI serial E<sup>2</sup>PROM.

#### Table 2.2 CPOL Options

| CPOL | Description           |

|------|-----------------------|

| 0    | Clock line idles low  |

| 1    | Clock line idles high |

The synchronous serial port on the H8/3644 conforms to the CPOL = 1 setting because the  $SCK_1$  line idles high.

#### Table 2.3 CPHA Options

| СРНА | Description                                                                  |

|------|------------------------------------------------------------------------------|

| 1    | SI data latched on rising edge of SCK SO data updated on falling edge of SCK |

| 0    | SI data latched on falling edge of SCK SO data updated on rising edge of SCK |

The synchronous serial port on the H8/3644 conforms to the CPHA = 1 setting. The SI<sub>1</sub> line is sampled on the rising edge of SCK<sub>1</sub>, and the SO<sub>1</sub> line is updated on the falling edge of SCK<sub>1</sub>.

The selection of register bits CPOL =1 and CPHA = 1 is called SPI mode 1,1. This is the SPI mode that the H8/3644 can emulate. Mode 1,1 SPI serial  $E^2$ PROMs can be read and written using the synchronous serial port SCI<sub>1</sub> on the H8/3644

## Section 3 SPI E<sup>2</sup>PROM Details

#### 3.1 The Commands

A microcontroller/SPI serial E<sup>2</sup>PROM interface is command driven. For example, to read data from the memory:

- 1. the microcontroller asserts the chip select line low

- 2. sends a READ command

- 3. sends the address of the desired data

- 4. Uses the clock line to shift the data in

- 5. At the end of the transaction, the microcontroller raises the chip select line

For an  $E^2PROM$  there are also commands to WRITE the memory array, read and write to a status register, and set and clear a write enable latch. See Table 3.1 for a list of the commands for the 25xx040  $E^2PROM$  that is used as the example in this application note.

| Instruction Name | Instruction Format      | Description                                               |

|------------------|-------------------------|-----------------------------------------------------------|

| READ             | 0000 A <sub>8</sub> 011 | Read data from memory array beginning at selected address |

| WRITE            | 0000 A <sub>8</sub> 010 | Write data to memory array beginning at selected address  |

| WRDI             | 0000 0100               | Reset the write enable latch (disable write operations)   |

| WREN             | 0000 0110               | Set the write enable latch (enable write operations)      |

| RDSR             | 0000 0101               | Read status register                                      |

| WRSR             | 0000 0001               | Write status register                                     |

|                  |                         |                                                           |

Note: A<sub>8</sub> is the 9<sup>th</sup> address bit necessary to fully address 512 bytes.

#### **3.2** The 25xx040 E<sup>2</sup>PROM

The Microchip 25xx040 is an example of a 4K bit (512 byte) Serial E<sup>2</sup>PROM that can interface directly with the SCI1 port on the H8/3644 microcontroller. As a review, the bus signals required are a clock input (SCK), data in (SI) and data out (SO) lines. Access to the device is controlled by a chip select (CS) input. The SCK is used to synchronize the communication between the H8/3644 and the 25xx040. Instructions, addresses, or data present on the SI pin are latched on the rising edge of the SCK input. Data is shifted out through the SO pin on the falling edge of the SCK.

The CS pin must be low and the HOLD pin must be high for the entire operation. The WP pin must be held high to allow writing to the memory array.

Communication to the device can be paused via the hold pin (HOLD). While the device is paused, transitions on its inputs will be ignored, with the exception of chip select, allowing the host to service higher priority interrupts. Also, write operations to the device can be disabled via the write protect pin (WP).

#### 3.3 Protocol

For the 25xx040 device because you need 9 bits to address the 512 bytes of memory, the most significant address bit (A8) is located in the instruction byte.

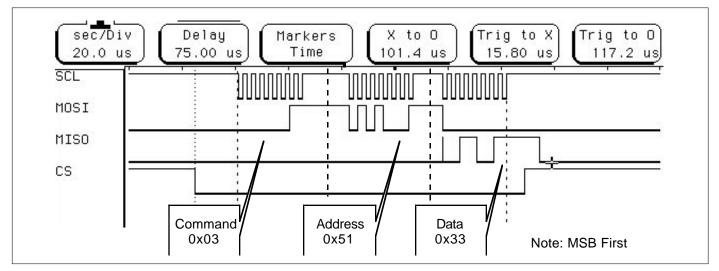

#### 3.3.1 Read Command Bus Timing

See Figure 3.1 for an example of what the READ command looks like on a logic analyzer. The first byte transferred on the MOSI (SO<sub>1</sub>) pin is the READ command. This is a command to read address 0x51 so A<sub>8</sub>, the most significant bit in the Address, is 0 in this case. So the first byte is 0x03. The second byte transferred on the MOSI pin contains the 8 low order address bits which are 0x51. The E<sup>2</sup>PROM puts the last byte, 0x33, on the MISO (SI<sub>1</sub>) pin.

Figure 3.1 Read Command Timing

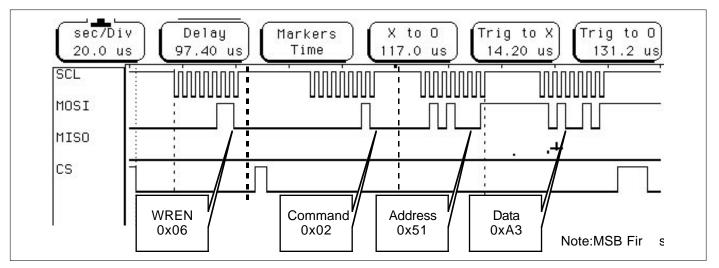

#### 3.3.2 Write Command Bus Timing

See Figure 3.2 for an example of what the timing looks like on a logic analyzer to write data to an SPI E<sup>2</sup>PROM. The first byte transferred on the MOSI (SO<sub>1</sub>) pin is the write latch enable (WREN) command, 0x06. The next byte transferred on the MOSI (SO<sub>1</sub>) pin is the WRITE command. This is a command to write to address 0x51 so  $A_8 = 0$ . The second byte is 0x02. The third byte transferred contains the 8 low order address bits which are 0x51. The last byte, 0xa3, is the data to be written into address 0x51.

Figure 3.2 Write Command Timing

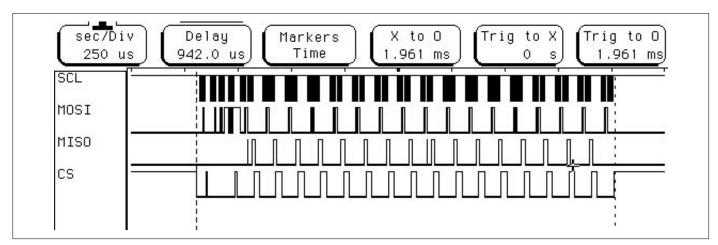

#### 3.3.3 Write Command Polling

See Figure 3.3 to get an idea of the relative time it takes to write one memory location, This logic analyzer trace shows that total time from the WREN command until the read status register command (RDSR) says that the write is complete is 1.96 ms.

Figure 3.3 Write Command Timing (To Completion)

## Section 4 SCI1 Operation

#### 4.1 Hardware Registers

SCI1 on the H8/3644 operates only in the synchronous mode. Table 4.1 lists the hardware registers for SCI1.

#### Table 4.1 SCI1 Registers

| Name                             | Abbrev. | R/W | Initial Value | Address |

|----------------------------------|---------|-----|---------------|---------|

| Serial control register 1        | SCR1    | R/W | H'00          | H'FFA0  |

| Serial control status register 1 | SCSR1   | R/W | H'9C          | H'FFA1  |

| Serial data register U           | SDRU    | R/W | Not fixed     | H'FFA2  |

| Serial data register L           | SDRL    | R/W | Not fixed     | H'FFA3  |

#### 4.1.1 Serial Control Register Bits

Serial Control Register 1 (SCR1) is the only SCI1 register that needs to be setup to initialize the H8/3644 to interface to a SPI  $E^2$ PROM. Below are the settings for the bits in the SCR1 register that are used in this application note.

SCR1: 0xFFA0

| 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|------|------|-------|------|------|------|------|------|

| SNC1 | SNC0 | MRKON | LTCH | CKS3 | CKS2 | CKS1 | CKS0 |

| 0    | 0    | 0     | 0    | 0    | 1    | 0    | 0    |

Note: CKS2 = 1,CKS1 = 0,CKS0 =  $0 \rightarrow 312.5 \text{ kHz SCK}_1$  (F = 5MHz)

The SCI1 port can transmit 16-bit data or 8-bit data. SCI1 should be setup to send 8-bit data to read and write to an SPI  $E^2$ PROM. Set SNC1 = 0 and SNC2 = 0 for 8-bit data transfers.

SCR1 can control multiple ICs using the Synchronized Serial Bus (SSB) communication's protocol. Make sure that MRKON = 0 to disable the SSB communication's protocol.

SCI1 can operate with an internal or external clock selected as the clock source. The H8/3644 should generate the clock from the internal prescaler and output the clock signal on the SCK<sub>1</sub> pin. Set the CKS3 = 0 to select the internal clock. Set CKS2-CKS0 to select a prescaler division value that gives the correct bit rate.

Writing data to SCR1 when bit MRKON in SCR1 is cleared to 0 initializes the internal state of SCI1.

#### 4.1.2 Port Mode Register 3

In addition, the I/O pins for  $SO_1$ ,  $SI_1$  and  $SCK_1$  have to be enable in Port Mode Register 3 (PMR3) for use as serial port pins. See below.

PMR3: 0xFFFD

| 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0    |

|---|---|---|---|---|-----|-----|------|

|   |   |   |   |   | SO1 | SI1 | SCK1 |

| 0 | 0 | 0 | 0 | 0 | 1   | 1   | 1    |

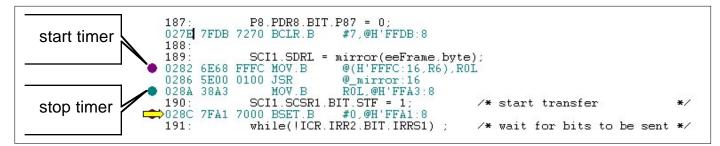

#### 4.2 Data Transfer Operations

The protocol for an H8/3644 to communicate with an SPI E<sup>2</sup>PROM requires the simultaneous transmission and reception of data using SCI1.

A simultaneous transmit/receive operation is carried out as follows:

- 1. Write transmit data in SDRL.

- 2. Set the SCSR1 start flag (STF) bit to 1.

SCI1 starts operating.

Transmit data is output at pin SO1.

Receive data is input at pin SI1.

- 3. After data transmission and reception are complete, bit IRRS1 in IRR2 is set to 1.

- 4. Read the received data from SDRL

#### 4.2.1 Serial Control/Status Register Bits

SCSR1: 0xFFA1

| 7 | 6   | 5    | 4 | 3 | 2 | 1    | 0   |  |

|---|-----|------|---|---|---|------|-----|--|

|   | SOL | ORER |   |   |   | MTRF | STF |  |

| 1 | 0   | 0    | 1 | 1 | 1 | 0    | 0   |  |

Note: Initial values

#### 4.2.2 Interrupt Request Register 2

IRR2: 0xFFF8

| 7     | 6     | 5 | 4     | 3 | 2 | 1    | 0   |

|-------|-------|---|-------|---|---|------|-----|

| IRRDT | IRRAD |   | IRRS1 |   |   | MTRF | STF |

| 0     | 0     | 0 | 0     | 0 | 0 | 0    | 0   |

Note: Initial values

IRRS1 is set to 1 when an SCI1 interrupt is requested. The flag is not cleared automatically when an interrupt is accepted. It is necessary to write 0 to clear the flag.

After data transmission is complete, the serial clock is not output until the next time the start flag is set to 1. During this time, pin SO<sub>1</sub> continues to output the value of the last bit transmitted.

## Section 5 Test Hardware

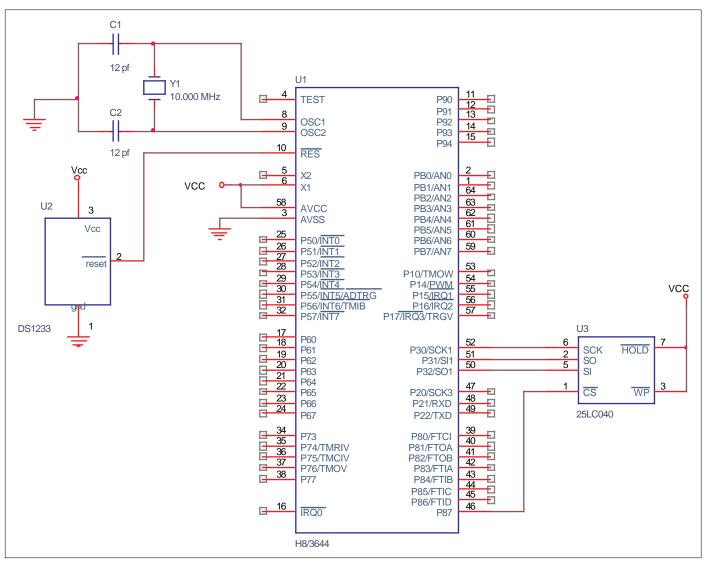

Figure 5.1 is the schematic showing the basic components for a representative circuit that can connect a Hitachi H8/3644 microcontroller to a  $25xx040 E^2$ PROM. A DS1233 low cost power supply monitor/reset IC improves the reliability of the  $E^2$ PROM data. If the power supply voltage drops below the minimum value for Vcc, then the H8/3644 will be reset. before it can execute random code that might write erroneous data to the  $E^2$ PROM.

Figure 5.1 Hardware Block Diagram

In this design, I/O port 8 pin 7 is configured as an output and is used as the chip select for the 25LC040  $E^2$ PROM. The HOLD and WP functions of the  $E^2$ PROM are not used in this example, and the control pins for those functions are tied to their inactive voltage state, Vcc.

## Section 6 Software Details

#### 6.1 Bit Reverse Function

The SPI serial  $E^2$ PROM communications protocol specifies that data will be transmitted starting with the most significant bit first. In synchronous mode the SCI interfaces on H8 microcontrollers shift data in and out starting with the least significant bit first. The application software can rotate the data bits to adjust for the difference in the two specifications. The example code in 6.1.1 below shows two ways to implement a bit-reversal function in assembly language that you can call from your C code. 6.1.4 shows a bit-reverse function in C code.

#### 6.1.1 Bit-Reversal Source Code in Assembler

.section P,CODE,ALIGN=2

.export \_mirror

.export \_reverse

#### \_mirror:

rotxl.b r0h rotxr.b r0l rotxl.b r0h

rotxr.b r01

- rotxr.b r0l

- rotx1.b r0h

- rotxr.b r01

- rotxl.b r0h

- mov r0h,r0l

rts

#### \_reverse:

mov.b #8,r11

#### loop:

| rotxr.b | r01 |         |

|---------|-----|---------|

| rotxl.b | r0h |         |

| dec     | r11 |         |

| bne     |     | loop    |

| mov     |     | r0h,r0l |

| rts     |     |         |

| .END    |     |         |

#### 6.1.2 Example Declaration

Using the function mirror() as an example, the bit-reversal function is declared in you C code as:

extern unsigned char mirror(unsigned char);

#### 6.1.3 Design Tradeoffs

The function, mirror(), is optimized for speed of execution. The function, reverse(), is optimized for code size. The C function mirror2() was added to make the bit-reversal function more portable. Table 6.1 highlights the differences between the three example functions.

#### Table 6.1 Bit-Reversal Function Tradeoffs

| Function             | Size (bytes) <sup>1</sup> | Execution Speed (µsec)²<br>(F = 5 MHz) |  |

|----------------------|---------------------------|----------------------------------------|--|

| mirror               | 44                        | 11.2                                   |  |

| reverse              | 22                        | 21.2                                   |  |

| mirror2 <sup>3</sup> | 42                        | 38.8                                   |  |

Notes 1,2,3: Includes the overhead to call the function

Note 3: C code optimized for speed with register optimization on

Note: See Figure 6.1 for an example of how to fill-in the HiVIEW dialog box to generate C code that is optimized for speed with register optimization turned on.

This application note uses the function mirror() to reverse the bits. The bus timing examples show in Section 3 reflect the  $11.2 \,\mu$ seconds of overhead required to reverse the bits before they are written to the SCI1 data register in the H8/3466.

Figure 6.1 shows that the 11.2  $\mu$ seconds includes the overhead to call the function in C as well as the time it takes to execute the assembly language code in the functions themselves.

#### 12

Figure 6.1 Bit Reverse Function Timing Details

#### 6.1.4 Bit-Reversal Function in C

unsigned char mirror2(unsigned char value )

#### {

unsigned char inMask,outMask,i,reversed;

```

inMask = 0x01;

outMask = 0x80;

reversed = 0;

for(i=8;i>0;i--)

```

```

{

```

if(inMask & value)

reversed |= outMask;

```

inMask <<= 1;

```

outMask >>= 1;

}

```

return(reversed);

```

}

| General Compiler Assembler Linker Debug Custom Build                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ☑ ptimize code       Mul/div optimization         Speed optimizations:         ☑ Register         □ Shift         □ Loop         □ Switch         □ Inline         □ Struct |

| -CP=300L -DEB -COM -L=evb3644.lst -SP=RE<br>-DEF=EEPROM=46                                                                                                                  |

Figure 6.1 C Code Optimized for Speed

#### 6.2 E<sup>2</sup>PROM Interface C Functions

After eepromInit() is called, the rest of the software for this application note is a just a collection of C functions that simultaneously transmit and receive 8 bit data using SCI1 on the H8/3644. The software functions are mostly just wrappers around the 25xx040 command set that is shown in Table 3.1. These basic example functions do not do error checking and do not return status codes.

Table 6.2 provides a summary for the C functions that interface the H8/3644 to the Microchip  $25xx040 E^2$ PROM in this application note.

| Function                              | Description                                                                                                                              |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| void eepromInit(void);                | Must be called first                                                                                                                     |

|                                       | Initialize H8/3644 SCI1 for 8 bit synchronous operation                                                                                  |

|                                       | Initialize I/O pin used for E <sup>2</sup> PROM chip select                                                                              |

|                                       | Initialize E <sup>2</sup> PROM by toggling the chip select to enter active state                                                         |

| BYTE Read(WORD address);              | Uses the READ command to return the byte at an E <sup>2</sup> PROM address                                                               |

| void Write(WORD address, BYTE value); | Uses the WRITE command to write a byte to an E <sup>2</sup> PROM address                                                                 |

|                                       | The function does not return until the write operation has completed.                                                                    |

| Void WriteEnable(void);               | Enables WRITE commands                                                                                                                   |

|                                       | Normally only called by the function Write()                                                                                             |

|                                       | The WREN command must be sent to the E <sup>2</sup> PROM before the E <sup>2</sup> PROM will execute a WRITE command                     |

| void WriteDisable(void);              | Uses the WRDI command to disable WRITE commands                                                                                          |

|                                       | Normally does not need to be called by the user                                                                                          |

|                                       | After executing a WRITE command, the E <sup>2</sup> PROM automatically disables further WRITE commands.                                  |

| BYTE ReadStatus();                    | Uses the RDSR command to read the status register                                                                                        |

|                                       | The function Write() calls ReadStatus() repeatedly to poll the write in progress bit until the write operation completes                 |

| void WriteProtect( PROTECTION value); | Uses the WRSR command to write to the bits in the status register that write protect sections of the E <sup>2</sup> PROM's memory array. |

#### Table 6.2 E<sup>2</sup>PROM Interface Functions Summary

The example hardware/software design in this application note includes just the basics on how to use the H8/3644 SCI1 interface to read and write data using a SPI  $E^2$ PROM. If you feel you need additional write protection security, you can use software to control an I/O pin that is connected the WP pin on the 25xx040.

The source code for the  $E^2PROM$  interface functions can be found in Appendix A of this application note. The header file can be found in Appendix B.

## Appendix A Code

#include "ee3644.h"

extern unsigned char mirror(unsigned char);

typedef unsigned char BYTE; typedef unsigned int WORD;

typedef enum protectionn\_tag

{

NONE = 0, /\* none \*/ QUARTER = 1,/\* 0x180 - 0x1ff \*/ HALF = 2, /\* 0x100 - 0x1ff \*/ ALL = 3 /\* 0x000 - 0x1ff \*/

}PROTECTION;

typedef enum Instruction\_tag

{

{

READ = 3, WRITE = 2, WRDI = 4, WREN = 6, RDSR = 5, WRSR = 1

#### }INSTRUCTION;

typedef union header\_tag unsigned char byte; struct { unsigned int Space : 4; unsigned int AB8 : 1; unsigned int Opcode : 3; }fields;

#### }HEADER;

```

typedef union status_tag

{

unsigned char byte;

struct {

unsigned char wk

:4;

unsigned char BP

:2;

unsigned char WEL

:1;

unsigned char WIP

:1;

}bits;

}STATUS;

```

```

/**********************************

```

```

* Function Prototypes *

\*******************************

```

void eepromInit(void); void WriteEnable(void); void WriteDisable(void); BYTE Read(WORD address); void Write(WORD address, BYTE value); BYTE ReadStatus(); void WriteProtect( PROTECTION value); unsigned char mirror2(unsigned char value );

```

/*****************

```

```

* Global Variables

\**********************/

```

BYTE value; INSTRUCTION instruction; WORD address; BYTE data; PROTECTION segment;

int main (void) {

eepromInit();

```

while (1)

```

{

```

address = 0x51;

data = 0x96;

instruction = READ;

value = 0xa5;

segment = NONE;

switch(instruction)

{

case READ:

data = Read(address);

break;

case WRITE:

Write(address,value);

break;

case WRDI:

WriteDisable();

break;

case WREN:

WriteEnable();

break;

```

\*

```

case RDSR:

data = ReadStatus();

break;

case WRSR:

WriteProtect(segment);

break;

};

}

return (0);

}

void eepromInit(void)

{

P8.PCR8.BIT.PCR87 = 1;

/* P8.7 is CS for eeprom

*/

PMR3.PMR.BIT.SO1 = 1;

/* turn on S0

*/

PMR3.PMR.BIT.SCK1 = 1;

/* turn on SCK

*/

PMR3.PMR.BIT.SI1 = 1;

/* turn on SI

*/

SCI1.SCR1.BIT.SNC = 0;

/* 8-bit synchronous transfer mode */

/* clock source is prescaler

SCI1.SCR1.BIT.CKS3 = 0;

*/

/* phi/16 clock

SCI1.SCR1.BIT.CKS = 4;

*/

P8.PDR8.BIT.P87 = 0;

/* toggle CS after power-up

*/

P8.PDR8.BIT.P87 = 1;

}

void WriteEnable(void)

{

P8.PDR8.BIT.P87 = 0;

/* chip select

*/

SCI1.SDRL = mirror(WREN);

SCI1.SCSR1.BIT.STF = 1;

/* start transfer

*/

/* wait for bits to be sent

while(!ICR.IRR2.BIT.IRRS1);

*/

ICR.IRR2.BIT.IRRS1 = 0;

P8.PDR8.BIT.P87 = 1;

}

void WriteDisable(void)

{

P8.PDR8.BIT.P87 = 0;

SCI1.SDRL = mirror(WRDI);

SCI1.SCSR1.BIT.STF = 1;

*/

/* start transfer

while(!ICR.IRR2.BIT.IRRS1);

/* wait for bits to be sent

*/

ICR.IRR2.BIT.IRRS1 = 0;

P8.PDR8.BIT.P87 = 1;

```

```

HITACHI

```

}

```

BYTE Read(WORD address)

```

{

```

HEADER eeFrame;

```

eeFrame.byte = 0; eeFrame.fields.AB8 = (address > 0xff); eeFrame.fields.Opcode = READ;

P8.PDR8.BIT.P87 = 0;

SCI1.SDRL = mirror(eeFrame.byte); SCI1.SCSR1.BIT.STF = 1; while(!ICR.IRR2.BIT.IRRS1) ; ICR.IRR2.BIT.IRRS1 = 0; SCI1.SDRL = mirror((address & 0xff)); SCI1.SCSR1.BIT.STF = 1; while(!ICR.IRR2.BIT.IRRS1) ; ICR.IRR2.BIT.IRRS1 = 0; SCI1.SCSR1.BIT.STF = 1; while(!ICR.IRR2.BIT.IRRS1) ; ICR.IRR2.BIT.IRRS1 = 0;

| /* start transfer<br>/* wait for bits to be sent | */ | */ |    |

|--------------------------------------------------|----|----|----|

| /* low order address bits<br>/* start transfer   | */ | */ |    |

| /* wait for bits to be sent                      | */ | ~/ |    |

| /* clock in data<br>/* start transfer            |    | */ | */ |

| /* wait for bits to be sent                      | */ |    |    |

P8.PDR8.BIT.P87 = 1;

return(mirror(SCI1.SDRL));

#### }

BYTE ReadStatus()

{

HEADER eeFrame;

eeFrame.byte = 0; eeFrame.fields.Opcode = RDSR;

P8.PDR8.BIT.P87 = 0;

```

SCI1.SDRL = mirror(eeFrame.byte);SCI1.SCSR1.BIT.STF = 1;while(!ICR.IRR2.BIT.IRRS1);/* start transfer/* wait for bits to be sent */ICR.IRR2.BIT.IRRS1 = 0;SCI1.SDRL = 0;/* clock in dataSCI1.SCSR1.BIT.STF = 1;/* start transfer*/while(!ICR.IRR2.BIT.IRRS1);/* wait for bits to be sent */ICR.IRR2.BIT.IRRS1 = 0;

```

P8.PDR8.BIT.P87 = 1;

return(mirror(SCI1.SDRL));

HITACHI

\*/

```

}

void WriteProtect(PROTECTION value)

{

HEADER eeFrame;

STATUS eeStatus;

eeFrame.byte = 0;

eeFrame.fields.AB8 = (address > 0xff);

eeFrame.fields.Opcode = WRSR;

eeStatus.byte = 0;

eeStatus.bits.BP = value;

WriteEnable();

P8.PDR8.BIT.P87 = 0;

SCI1.SDRL = mirror(eeFrame.byte);

SCI1.SCSR1.BIT.STF = 1;

/* start transfer

*/

while(!ICR.IRR2.BIT.IRRS1);

/* wait for bits to be sent */

ICR.IRR2.BIT.IRRS1 = 0;

SCI1.SDRL = mirror(eeStatus.byte);

/* low order addrress bits */

SCI1.SCSR1.BIT.STF = 1;

/* start transfer

*/

while(!ICR.IRR2.BIT.IRRS1);

/* wait for bits to be sent */

ICR.IRR2.BIT.IRRS1 = 0;

P8.PDR8.BIT.P87 = 1;

while(ReadStatus() & 0x01);

/* wait for programming

*/

}

void Write(WORD address, BYTE value)

{

HEADER eeFrame;

eeFrame.byte = 0;

eeFrame.fields.AB8 = (address > 0xff);

eeFrame.fields.Opcode = WRITE;

WriteEnable();

P8.PDR8.BIT.P87 = 0;

SCI1.SDRL = mirror(eeFrame.byte);

SCI1.SCSR1.BIT.STF = 1;

/* start transfer

*/

while(!ICR.IRR2.BIT.IRRS1);

/* wait for bits to be sent */

ICR.IRR2.BIT.IRRS1 = 0;

/* low order addrress bits

*/

SCI1.SDRL = mirror(address & 0xff);

SCI1.SCSR1.BIT.STF = 1;

/* start transfer

*/

while(!ICR.IRR2.BIT.IRRS1);

/* wait for bits to be sent */

```

HITACHI

/\* clock out data

\*/

ICR.IRR2.BIT.IRRS1 = 0;

SCI1.SDRL = mirror(value);

```

SCI1.SCSR1.BIT.STF = 1;

/* start transfer

*/

while(!ICR.IRR2.BIT.IRRS1);

/* wait for bits to be sent */

ICR.IRR2.BIT.IRRS1 = 0;

P8.PDR8.BIT.P87 = 1;

while(ReadStatus() & 0x01);

/* wait for programming

*/

unsigned char mirror2(unsigned char value )

unsigned char inMask,outMask,i,reversed;

inMask =

0x01;

outMask =

0x80;

reversed = 0;

for(i=8;i>0;i--)

{

if(inMask & value)

reversed |= outMask;

inMask <<= 1;

outMask >>= 1;

}

return(reversed);

```

}

{

}

## Appendix B Header Files

#### #ifndef \_\_evb3644\_\_\_ #define \_\_evb3644\_\_\_

struct st\_icr {

\*/ /\* IEGR1 union { unsigned char BYTE; /\* Byte Access \*/ struct { /\* Bit Access \*/ unsigned char wk :4; unsigned char IEG3 :1; unsigned char IEG2 :1; unsigned char IEG1 :1; unsigned char IEG0 :1; BIT; } } IEGR1; \*/ /\* IEGR2 union { unsigned char BYTE; /\* Byte Access \*/ struct { /\* Bit Access \*/ unsigned char INTEG7 :1; unsigned char INTEG6 :1; unsigned char INTEG5 :1; unsigned char INTEG4 :1; unsigned char INTEG3 :1; unsigned char INTEG2 :1; unsigned char INTEG1 :1; unsigned char INTEG0 :1; BIT; IEGR2; } /\* IENR1 \*/ union { unsigned char BYTE; /\* Byte Access \*/ struct { /\* Bit Access \*/ unsigned char IENTB1 :1; unsigned char IENTA :1; :2; unsigned char wk0 unsigned char IEN3 :1; unsigned char IEN2 :1; unsigned char IEN1 :1; unsigned char IEN0 :1; BIT; } IENR1; } /\* IENR2 \*/ union { unsigned char BYTE; /\* Byte Access \*/ struct { /\* Bit Access \*/ unsigned char IENDT :1; unsigned char IENAD :1; unsigned char wk1 :1; unsigned char IENS1 :1;

} BIT; IRR3; }

};

struct st\_sci1 {

|                                                                    | union {<br>unsigned char BYTE;<br>struct {<br>unsigned char SNC<br>unsigned char MRH<br>unsigned char LTC<br>unsigned char CKS<br>unsigned char CKS<br>BIT;<br>}<br>SCR1;                | XON :1;<br>H :1;<br>3 :1;                          |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                    | union<br>unsigned char BYTE;<br>struct {<br>unsigned char wk :<br>unsigned char SOL<br>unsigned char ORE<br>unsigned char Wk1<br>unsigned char MTH<br>unsigned char STF<br>}<br>BIT<br>} | :1;<br>R :1;<br>:3;                                |

| };<br>struct st_pm3 {<br>union {<br>unsig<br>struc                 | unsigned char wk :5;<br>unsigned char SO1 :1;<br>unsigned char SI1 :1;                                                                                                                   | /* PMR */<br>.ccess */<br>/* Bit Access */         |

| }BIT<br>} PMR<br>};<br>struct st_p8 {<br>union {<br>unsig<br>struc | R;<br>gned char BYTE; /                                                                                                                                                                  | /* PDR8 */<br>* Byte Access */<br>/* Bit Access */ |

unsigned char P83:1; unsigned char P82:1; unsigned char P81:1; unsigned char P80:1; BIT; } PDR8 } ; wk3[15]; char /\* PCR8 \*/ union { unsigned char BYTE; /\* Byte Access \*/ /\* Bit Access \*/ struct { unsigned char PCR87:1; unsigned char PCR86:1; unsigned char PCR85:1; unsigned char PCR84:1; unsigned char PCR83:1; unsigned char PCR82:1; unsigned char PCR81:1; unsigned char PCR80:1; BIT; } } PCR8 ; }; #define SCI1 (\*(volatile struct st\_sci1 /\* SCI1 Addr A0 \*/ \*)0xFFA0) #define PMR3 (\*(volatile struct st\_pm3) \*)0xFFFD) /\* PMR3 Address \*/ #define ICR (\*(volatile struct st\_icr \*)0xFFF2) /\* ICR Address \*/

#define P8 (\*(volatile struct st\_p8 \*)0xFFDB) /\* P8 Addr DB

#endif

\*/