# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

## HEF4094B MSI

### 8-STAGE SHIFT-AND-STORE BUS REGISTER

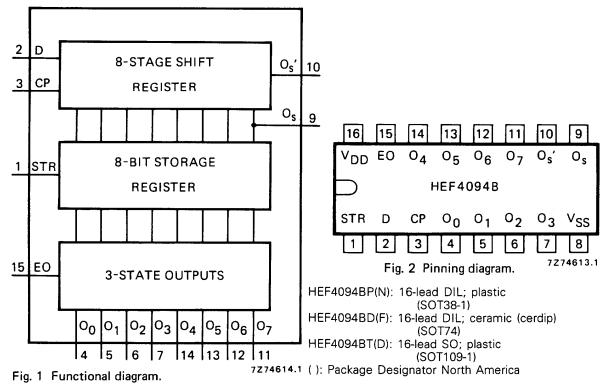

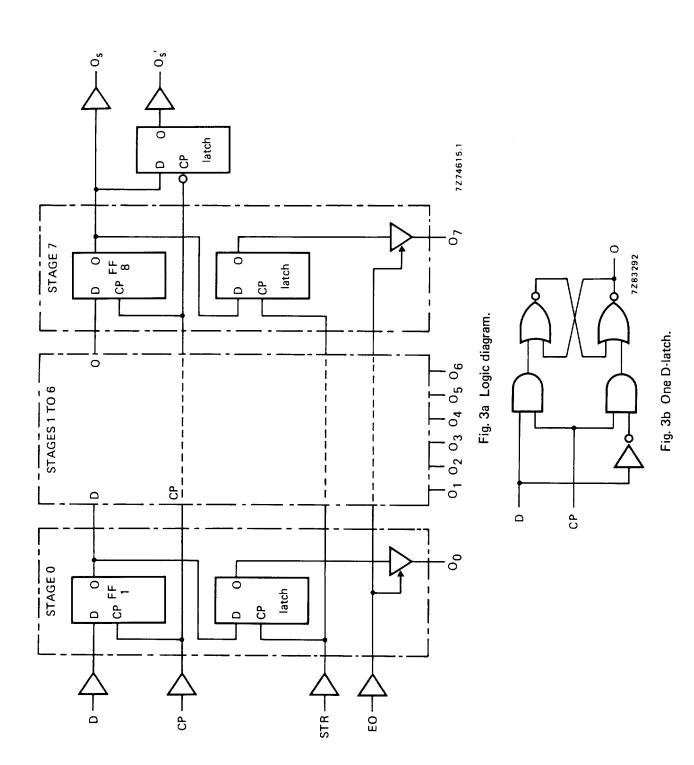

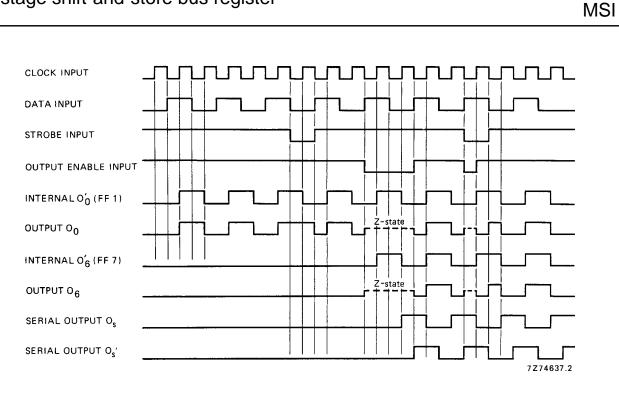

The HEF4094B is an 8-stage serial shift register having a storage latch associated with each stage for strobing data from the serial input to parallel buffered 3-state outputs  $O_0$  to  $O_7$ . The parallel outputs may be connected directly to common bus lines. Data is shifted on positive-going clock transitions. The data in each shift register stage is transferred to the storage register when the strobe (STR) input is HIGH. Data in the storage register appears at the outputs whenever the output enable (EO) signal is HIGH.

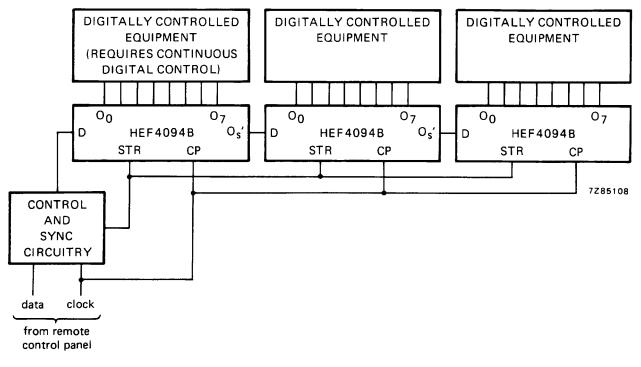

Two serial outputs ( $O_s$  and  $O'_s$ ) are available for cascading a number of HEF4094B devices. Data is available at  $O_s$  on positive-going clock edges to allow high-speed operation in cascaded systems in which the clock rise time is fast. The same serial information is available at  $O'_s$  on the next negative-going clock edge and provides cascading HEF4094B devices when the clock rise time is slow.

#### PINNING

| D   | data input   | EO                               | output enable input |

|-----|--------------|----------------------------------|---------------------|

| СР  | clock input  | 0 <sub>s</sub> , 0' <sub>s</sub> | serial outputs      |

| STR | strobe input | 0 <sub>0</sub> to 0 <sub>7</sub> | parallel outputs    |

FAMILY DATA

see Family Specifications

IDD LIMITS category MSI

January 1995

## HEF4094B MSI

# 8-stage shift-and-store bus register

HEF4094B MSI

#### FUNCTION TABLE

| inputs                     |                            |       | parallel    | outputs                | serial outputs                     |                                 |                                  |

|----------------------------|----------------------------|-------|-------------|------------------------|------------------------------------|---------------------------------|----------------------------------|

| СР                         | EO                         | STR   | D           | 0 <sub>0</sub>         | 0 <sub>n</sub>                     | 0 <sub>s</sub>                  | O's                              |

| ∫<br>↓<br>∫<br>↓<br>↓<br>↓ | L<br>L<br>H<br>H<br>H<br>H | ХХГНН | X X X L H H | Z<br>Z<br>L<br>H<br>nc | Z<br>Z<br>nc<br>On-1<br>On-1<br>nc | 0,6<br>nc,6<br>0,6<br>0,6<br>nc | nc<br>O7<br>nc<br>nc<br>nc<br>O7 |

H = HIGH state (the more positive voltage)

- L = LOW state (the less positive voltage)

- X = state is immaterial

- f = positive-going transition

- $\lambda$  = negative-going transition

- Z = high impedance off state

- nc = no change

- $O_6'$  = the information in the seventh shift register stage

At the positive clock edge the information in the 7th register stage is transferred to the 8th register stage and the  $O_s$  output.

#### A.C. CHARACTERISTICS

$V_{SS} = 0 V$ ;  $T_{amb} = 25$  °C; input transition times  $\leq 20$  ns

|                                                 | V <sub>DD</sub><br>V | typical formula for P ( $\mu$ W)                                                                                                                                                                       | where<br>$f_i = input freq. (MHz)$                                                                                                |

|-------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Dynamic power<br>dissipation per<br>package (P) | 5<br>10<br>15        | $\begin{array}{c} 2100 \; f_{i} + \Sigma(f_{o}C_{L}) \times V_{DD}^{2} \\ 9700 \; f_{i} + \Sigma(f_{o}C_{L}) \times V_{DD}^{2} \\ 26\;000 \; f_{i} + \Sigma(f_{o}C_{L}) \times V_{DD}^{2} \end{array}$ | $f_o =$ output freq. (MHz)<br>$C_L =$ load capacitance (pF)<br>$\Sigma(f_oC_L) =$ sum of outputs<br>$V_{DD} =$ supply voltage (V) |

## HEF4094B MSI

### A.C. CHARACTERISTICS

$V_{SS} = 0 \text{ V}; \text{ T}_{amb} = 25 \text{ }^{o}\text{C}; \text{ C}_{L} = 50 \text{ pF}; \text{ input transition times} \leq 20 \text{ ns}$

|                                                          | V <sub>DD</sub><br>V | symbol           | typ.            | max.              |                | typical extrapolation<br>formula                                                                                   |

|----------------------------------------------------------|----------------------|------------------|-----------------|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------|

| Propagation delays<br>CP — O <sub>s</sub><br>HIGH to LOW | 5<br>10<br>15        | tPHL             | 135<br>65<br>50 | 270<br>130<br>100 | ns<br>ns<br>ns | 108 ns + (0,55 ns/pF) CL<br>54 ns + (0,23 ns/pF) CL<br>42 ns + (0,16 ns/pF) CL                                     |

| LOW to HIGH                                              | 5<br>10<br>15        | <sup>t</sup> PLH | 105<br>50<br>40 | 210<br>100<br>80  | ns<br>ns<br>ns | 78 ns + (0,55 ns/pF) C <sub>L</sub><br>39 ns + (0,23 ns/pF) C <sub>L</sub><br>32 ns + (0,16 ns/pF) C <sub>L</sub>  |

| CP → O's<br>HIGH to LOW                                  | 5<br>10<br>15        | <sup>t</sup> PHL | 105<br>50<br>40 | 210<br>100<br>80  | ns<br>ns<br>ns | 78 ns + (0,55 ns/pF) C <sub>L</sub><br>39 ns + (0,23 ns/pF) C <sub>L</sub><br>32 ns + (0,16 ns/pF) C <sub>L</sub>  |

| LOW to HIGH                                              | 5<br>10<br>15        | <sup>t</sup> PLH | 105<br>50<br>40 | 210<br>100<br>80  | ns<br>ns<br>ns | 78 ns + (0,55 ns/pF) C <sub>L</sub><br>39 ns + (0,23 ns/pF) C <sub>L</sub><br>32 ns + (0,16 ns/pF) C <sub>L</sub>  |

| CP → O <sub>n</sub><br>HIGH to LOW                       | 5<br>10<br>15        | <sup>t</sup> PHL | 165<br>75<br>55 | 330<br>150<br>110 | ns<br>ns<br>ns | 138 ns + (0,55 ns/pF) CL<br>64 ns + (0,23 ns/pF) CL<br>47 ns + (0,16 ns/pF) CL                                     |

| LOW to HIGH                                              | 5<br>10<br>15        | <sup>t</sup> PLH | 150<br>70<br>55 | 300<br>140<br>110 | ns<br>ns<br>ns | 123 ns + (0,55 ns/pF) C <sub>L</sub><br>59 ns + (0,23 ns/pF) C <sub>L</sub><br>47 ns + (0,16 ns/pF) C <sub>L</sub> |

| STR ─► O <sub>n</sub><br>HIGH to LOW                     | 5<br>10<br>15        | <sup>t</sup> PHL | 110<br>50<br>35 | 220<br>100<br>70  | ns<br>ns<br>ns | 83 ns + (0,55 ns/pF) CL<br>39 ns + (0,23 ns/pF) CL<br>27 ns + (0,16 ns/pF) CL                                      |

| LOW to HIGH                                              | 5<br>10<br>15        | <sup>t</sup> PLH | 100<br>45<br>35 | 200<br>90<br>70   | ns<br>ns<br>ns | 73 ns + (0,55 ns/pF) CL<br>34 ns + (0,23 ns/pF) CL<br>27 ns + (0,16 ns/pF) CL                                      |

| Output transition<br>times<br>HIGH to LOW                | 5<br>10<br>15        | <sup>t</sup> THL | 60<br>30<br>20  | 120<br>60<br>40   | ns<br>ns<br>ns | 10 ns + (1,0 ns/pF) CL<br>9 ns + (0,42 ns/pF) CL<br>6 ns + (0,28 ns/pF) CL                                         |

| LOW to HIGH                                              | 5<br>10<br>15        | <sup>t</sup> TLH | 60<br>30<br>20  | 120<br>60<br>40   | ns<br>ns<br>ns | 10 ns + (1,0 ns/pF) CL<br>9 ns + (0,42 ns/pF) CL<br>6 ns + (0,28 ns/pF) CL                                         |

### HEF4094B MSI

### A.C. CHARACTERISTICS

$V_{\mbox{\scriptsize SS}}$  = 0 V;  $T_{\mbox{\scriptsize amb}}$  = 25 °C;  $C_{\mbox{\scriptsize L}}$  = 50 pF; input transition times  $\leqslant$  20 ns

|                                                    | V <sub>DD</sub><br>V | symbol             | min.           | typ.           | max.            |                   |  |  |

|----------------------------------------------------|----------------------|--------------------|----------------|----------------|-----------------|-------------------|--|--|

| 3-state propagation delays                         |                      |                    |                |                |                 |                   |  |  |

| Output enable times<br>EO — O <sub>n</sub><br>HIGH | 5<br>10<br>15        | <sup>t</sup> PZH   |                | 40<br>25<br>20 | 80<br>50<br>40  | ns<br>ns<br>ns    |  |  |

| LOW                                                | 5<br>10<br>15        | <sup>t</sup> PZL   |                | 40<br>25<br>20 | 80<br>50<br>40  | ns<br>ns<br>ns    |  |  |

| Output disable times<br>EO O <sub>n</sub><br>HIGH  | 5<br>10<br>15        | <sup>t</sup> PHZ   |                | 75<br>40<br>30 | 150<br>80<br>60 | ns<br>ns<br>ns    |  |  |

| LOW                                                | 5<br>10<br>15        | <sup>t</sup> PLZ   |                | 80<br>40<br>30 | 160<br>80<br>60 | ns<br>ns<br>ns    |  |  |

| Minimum clock<br>pulse width<br>LOW                | 5<br>10<br>15        | <sup>t</sup> WCPL  | 60<br>30<br>24 | 30<br>15<br>12 |                 | ns<br>ns<br>ns    |  |  |

| Minimum strobe<br>pulse width<br>HIGH              | 5<br>10<br>15        | <sup>t</sup> wstrh | 40<br>30<br>24 | 20<br>15<br>12 |                 | ns<br>ns<br>ns    |  |  |

| Set-up times<br>D CP                               | 5<br>10<br>15        | t <sub>su</sub>    | 60<br>20<br>15 | 30<br>10<br>5  |                 | ns<br>ns<br>ns    |  |  |

| Hold times<br>D — CP                               | 5<br>10<br>15        | <sup>t</sup> hold  | 5<br>20<br>20  | -15<br>5<br>5  |                 | ns<br>ns<br>ns    |  |  |

| Maximum clock<br>pulse frequency                   | 5<br>10<br>15        | f <sub>max</sub>   | 5<br>11<br>14  | 10<br>22<br>28 |                 | MHz<br>MHz<br>MHz |  |  |

HEF4094B

# 8-stage shift-and-store bus register

### HEF4094B MSI

### APPLICATION INFORMATION

Some examples of applications for the HEF4094B are:

- Serial-to-parallel data conversion

- Remote control holding register

Fig. 5 Remote control holding register.